Apr

13

Paper available at IEEE Latin American Transactions

April 13, 2024 | | Comments Off on Paper available at IEEE Latin American Transactions

The paper entitled “A Proposal of an ECC-based Adaptive Fault-Tolerant Mechanism for 16-bit data words”, written by J. Gracia-Morán (ORCID), L. J. Saiz-Adalid (ORCID), J. C. Baraza-Calvo (ORCID), D. Gil-Tomás (ORCID) and P. J. Gil-Vicente (ORCID), can be accessed at IEEE Latin American Transactions.

Video abstract here.

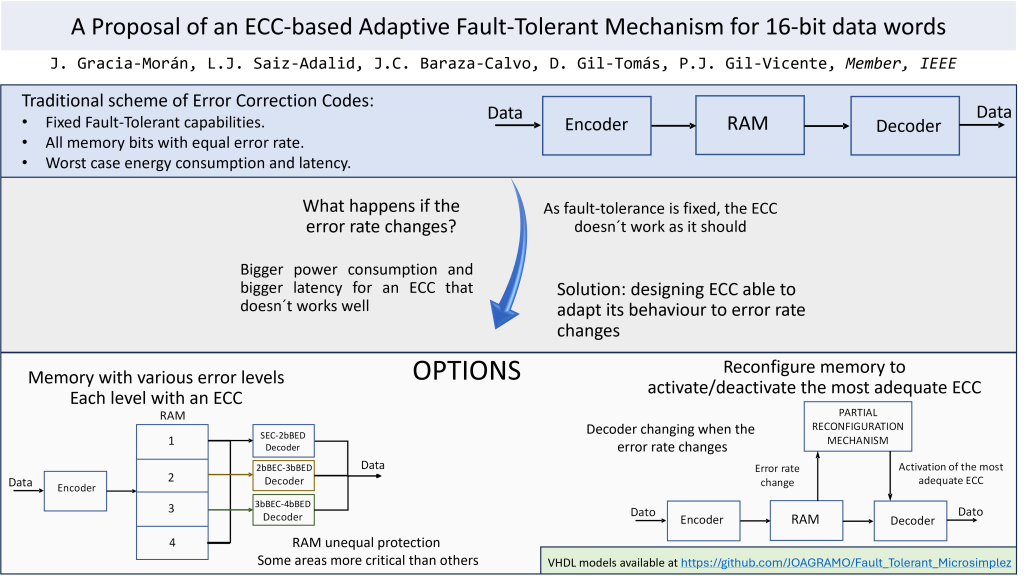

Graphical abstract:

Abstract

Actual memory systems provide large storage capacity thanks to the integration scale level achieved in CMOS technology. This increment in storage capacity comes with an augment on their fault rate. In this way, the probability of experiencing Single or Multiple Cell Upsets has risen. Error Correction Codes (ECC) are a fault-tolerant mechanism broadly employed to protect memory systems. Usually, an ECC-based fault tolerance mechanism is designed with fixed correction and detection capabilities. However, in some contexts, current memory systems can suffer a variable fault rate during their operation. Thus, it seems very interesting that this fault-tolerant mechanism would be able to adapt to these variable fault conditions.

This work proposes an Adaptive Fault-Tolerant mechanism based on ECC. This mechanism can adapt to different fault conditions, being able to correct and/or detect single and multiple bits in error. The Adaptive Fault-Tolerant mechanism proposed uses a unique encoder and various decoders. Therefore, there is no need to re-encode the data to change the error coverage since the unique encoder and the equal redundancy are the same regardless of the fault tolerance required. In addition, we have studied the area, delay, and power consumption overheads produced by the inclusion of the redundant bits, the encoder, and the decoders of the ECC in a computer system.

Comments