May

23

Paper available at IEEE early access

May 23, 2024 | | Comments Off on Paper available at IEEE early access

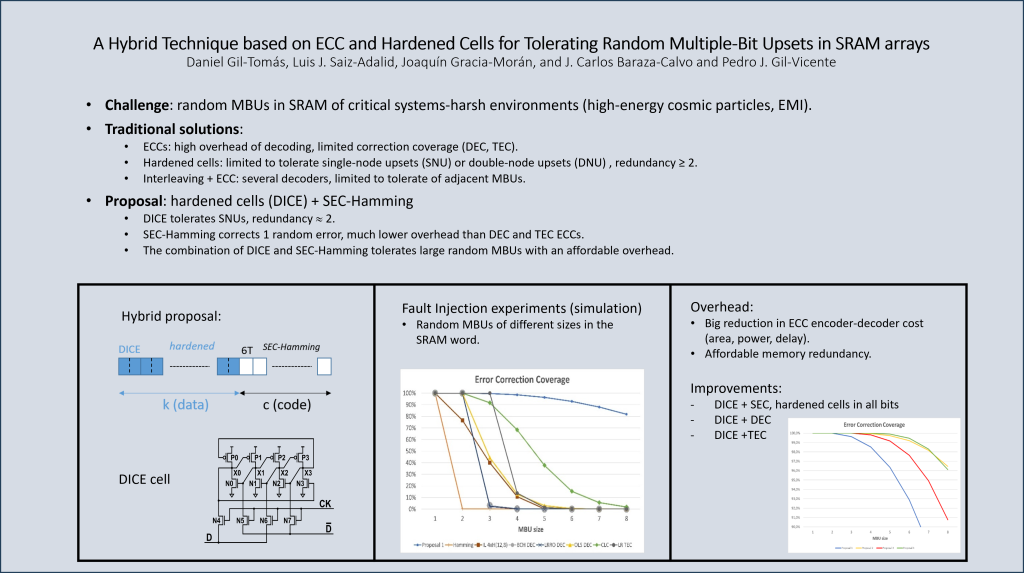

The paper entitled “A Hybrid Technique based on ECC and Hardened Cells for Tolerating Random Multiple-Bit Upsets in SRAM arrays”, written by Daniel Gil-Tomás, Luis J. Saiz-Adalid, Joaquín Gracia-Morán, J. Carlos Baraza-Calvo and Pedro J. Gil-Vicente is now available at IEEE Access.

Abstract:

MBU is an increasing challenge in SRAM memory, due to the chip’s large area of SRAM, and supply power scaling applied to reduce static consumption. Powerful ECCs can cope with random MBUs, but at the expense of complex encoding/decoding circuits, and high memory redundancy. Alternatively, radiation-hardened cell is an alternative technique that can mask single or even double node upsets in the same cell, but at the cost of increasing the overhead of the memory array. The idea of this work is to combine both techniques to take advantage of their respective strengths. To reduce redundancy and encoder/decoder overheads, SEC Hamming ECC has been chosen. About hardened cells, well-known and robust DICE cells, able to tolerate one node upset, have been used. To assess the proposed technique, we have measured the correction capability after a fault injection campaign, as well as the overhead (redundancy, area, power, and delay) of memory and encoding/decoding circuits. Results show high MBU correction coverages with an affordable overhead. For instance, for very harmful 8-bit random MBUs injected in the same memory word, more than 80% of the cases are corrected. Area overhead values of our proposal, measured with respect to double and triple error correction codes, are less than x1.45. To achieve the same correction coverage only with ECCs, redundancy, and overhead would be much higher.

Comments