Dec

11

Paper available at ACM

December 11, 2024 | | Comments Off on Paper available at ACM

The paper entitled “Allocating ECC parity bits into BF16-encoded CNN parameters: A practical experience report” written by Joaquín Gracia-Morán, Juan Carlos Ruiz Garcia, David de Andrés Martínez and Luis Jose Saiz-Adalid is available at ACM: https://dl.acm.org/doi/10.1145/3697090.3697092

Abstract

Using low-precision data types, like the Brain Floating Point 16 (BF16) format, can reduce Convolutional Neural Networks (CNNs) memory usage in edge devices without significantly affecting their accuracy. Adding in-parameter zero-space Error Correction Codes (ECCs) can enhance the robustness of BF16-based CNNs. However, implementing this technique raises practical questions. For instance, when the available invariant1 and non-significant2 bits in parameters for error correction are sufficient for the required protection level, the proper selection and combination of these bits become crucial. On the other hand, if the set of available bits is inadequate, converting nearly invariant bits to invariants might be considered. These decisions impact ECC decoder complexity and may affect the overall CNN performance. This report examines such implications using Lenet-5 and GoogLenet as case studies.

Oct

3

Paper accepted at LADC 2024

October 3, 2024 | | Comments Off on Paper accepted at LADC 2024

The paper entitled “Allocating ECC parity bits into BF16-encoded CNN parameters: A practical experience report” written by Joaquín Gracia-Morán, Juan Carlos Ruiz Garcia, David de Andrés Martínez and Luis Jose Saiz-Adalid has been accepted at 13th Latin-American Symposium on Dependable and Secure Computing (LADC 2024), that will be held in Recife (Brazil) next November.

Abstract

Using low-precision data types, like the Brain Floating Point 16 (BF16) format, can reduce Convolutional Neural Networks (CNNs) memory usage in edge devices without significantly affecting their accuracy. Adding in-parameter zero-space Error Correction Codes (ECCs) can enhance the robustness of BF16-based CNNs. However, implementing this technique raises practical questions. For instance, when the available invariant1 and non-significant2 bits in parameters for error correction are sufficient for the required protection level, the proper selection and combination of these bits become crucial. On the other hand, if the set of available bits is inadequate, converting nearly invariant bits to invariants might be considered. These decisions impact ECC decoder complexity and may affect the overall CNN performance. This report examines such implications using Lenet-5 and GoogLenet as case studies.

Oct

3

Paper available at Springer Link

October 3, 2024 | | Comments Off on Paper available at Springer Link

The paper entitled “In-Memory Zero-Space Floating-Point-based CNN protection using non-significant and invariant bits”, and written by Juan Carlos Ruiz Garcia, Luis Jose Saiz-Adalid, David de Andrés Martínez, and Joaquín Gracia-Morán, published at SAFECOMP 2024, can be accesed at this link.

Abstract

Convolutional Neural Networks (CNNs) have accomplished significant success in various domains, including transportation, health care and banking. Millions of weights, loaded from main memory into the internal buffers of CNN accelerators, are repeatedly used in the inference process. Accidental and malicious bit-flips targeting these buffers may negatively impact the CNN’s accuracy. This paper proposes a methodology to tolerate the effect of (multiple) bit-flips on floating-point-based CNNs using the non-significant and the invariant bits of CNN parameters. The former, determined after fault injection, do not significantly affect the accuracy of the inference process regardless of their value. The latter, determined after analyzing the network parameters, have the same value for all of them. Slight modifications can be applied to carefully selected parameters to increase the number of invariant bits. Since non-significant and invariant bits do not require protection against faults, they are employed to store the parity bits of error control codes. The methodology preserves the CNN accuracy, keeps its memory footprint, and does not require any retraining. Its usefulness is exemplished through the FP32 and BFloat16 versions of the LeNet-5 and GoogleNet CNNs.

Jul

12

25th anniverary of Instituto ITACA

July 12, 2024 | | Comments Off on 25th anniverary of Instituto ITACA

This year, we are celebrating the 25th anniversary of Instituto ITACA.

Congratulations!!

Jul

2

Presentation at IFIP WG 10.4 meeting

July 2, 2024 | | Comments Off on Presentation at IFIP WG 10.4 meeting

Juan C. Ruiz has presented the research work done by the Fault tolerant Systems research group of UPV at 86th IFIP WG 10.4 Meeting at Gold Coast, Australia, entitled “On improving the robustness of convolutional neural networks”.

Jun

28

CEDI 2024

June 28, 2024 | | Comments Off on CEDI 2024

Juan C. Ruiz, Luis J. Saiz and Joaquín Gracia have attended the CEDI 2024, that was held in A Coruña, Spain. During these days, they have contacted with others researches, exchanging ideas and establishing possible future collaborations

Jun

28

IFIP WG 10.4 meeting

June 28, 2024 | | Comments Off on IFIP WG 10.4 meeting

Juan C. Ruiz is attending the IFIP WG 10.4 meeting in Gold Coast, Australia. The IFIP WG 10.4 is aimed at identifying and integrating approaches, methods and techniques for specifying, designing, building, assessing, validating, operating and maintaining computer systems which should exhibit some or all of these attributes.

Jun

26

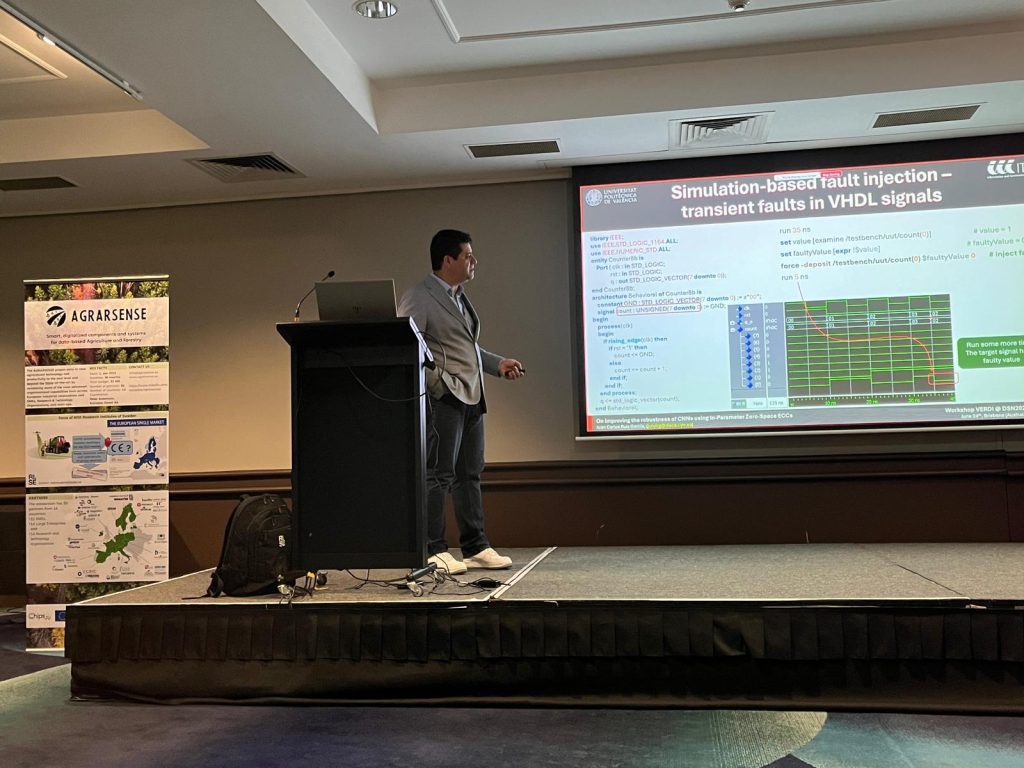

Invited speaker at DNS 2024

June 26, 2024 | | Comments Off on Invited speaker at DNS 2024

This June 24, the VERDI workshop (co-located with DSN 2024) was held in Brisbane, Australia. In this workshop, Juan C. Ruiz has been the invited speaker with a talk entitled “On improving the robustness of convolutional neural networks using in-parameter zero-space error correction codes“.

The program of VERDI 2024 can be seen here.

This talk has been sponsored by the Agencia Estatal de Investigación (Ministerio de Ciencia e Innovación) through the DEFADAS project.

Jun

26

Presentation at Jornadas SARTECO 2024 (III)

June 26, 2024 | | Comments Off on Presentation at Jornadas SARTECO 2024 (III)

J.C. Ruiz-García has presented the paper entitled “Tolerancia a fallos múltiples en redes convolucionales en coma flotante de 16 bits utilizando códigos correctores de errores”, authored by J.C. Ruiz-García, D. de Andrés Martínez, Luis J. Saiz-Adalid and J. Gracia-Morán at Jornadas SARTECO 2024 in A Coruña.

Jun

26

Presentation at Jornadas SARTECO 2024 (II)

June 26, 2024 | | Comments Off on Presentation at Jornadas SARTECO 2024 (II)

J. Gracia-Morán has presented the paper entitled “Protección mediante Códigos de Corrección de Errores de los pesos de una Red Neuronal implementada en Arduino”, authored by J. Gracia-Morán and Luis J. Saiz-Adalid at Jornadas SARTECO 2024 in A Coruña.